Works great simulates std_logic circuits just fine

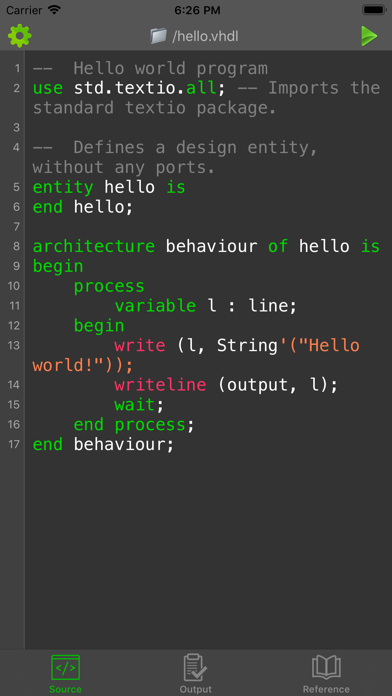

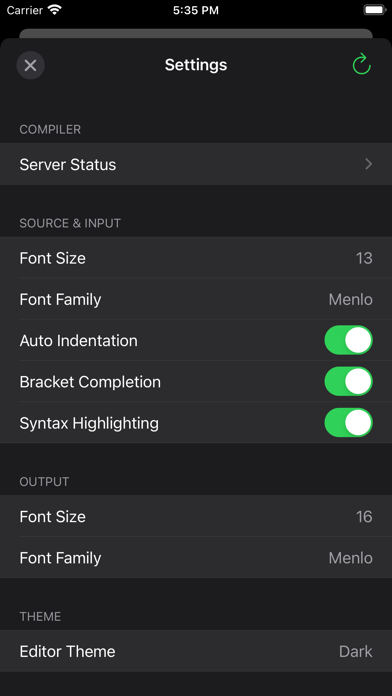

I realized that it’s essential to limit simulation with ultimately a WAIT; statement including a clock generator with limited total time Here is a simple test setup beyond just text: Enjoy.. great job by the developer of the App and the original open source VHDL Compiler Designer ———————————————— -- Hello world program library IEEE; use IEEE.std_logic_1164.all; use std.textio.all; -- Imports the standard textio package. -- Defines a design entity, without any ports. entity hello is end hello; architecture behaviour of hello is signal index : integer:=0; signal clk : std_logic := '0'; begin process(clk) variable l : line; begin if(rising_edge(clk)) then write(l,String'("/")); writeline (output, l); end if; end process; process begin index <= index +1; clk <= not clk; wait for 1 ns; if index > 20 then wait; end if; end process; end behaviour;